# HDL Coder™ Getting Started Guide

**R**2013**b**

# MATLAB®

#### **How to Contact MathWorks**

(a)

www.mathworks.comWebcomp.soft-sys.matlabNewsgroupwww.mathworks.com/contact\_TS.htmlTechnical Support

suggest@mathworks.com bugs@mathworks.com doc@mathworks.com service@mathworks.com info@mathworks.com Product enhancement suggestions Bug reports Documentation error reports Order status, license renewals, passcodes Sales, pricing, and general information

508-647-7000 (Phone) 508-647-7001 (Fax)

The MathWorks, Inc. 3 Apple Hill Drive Natick, MA 01760-2098

For contact information about worldwide offices, see the MathWorks Web site.

HDL Coder<sup>™</sup> Getting Started Guide

© COPYRIGHT 2012–2013 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

#### **Revision History**

| March 2012     | Online only |

|----------------|-------------|

| September 2012 | Online only |

| March 2013     | Online only |

| September 2013 | Online only |

New for Version 3.0 (Release 2012a) Revised for Version 3.1 (Release 2012b) Revised for Version 3.2 (Release 2013a) Revised for Version 3.3 (Release 2013b)

# Contents

### Getting Started with HDL Coder

| HDL Coder Product Description                  | 1-2<br>1-2 |

|------------------------------------------------|------------|

| Prepare Simulink Model For HDL Code Generation | 1-3        |

| Tool Setup                                     | 1-4        |

| C/C++ Compiler Setup                           | 1-4        |

| Synthesis Tool Path Setup                      | 1-4        |

| HDL Simulator Setup                            | 1-7        |

| Xilinx System Generator Setup                  | 1-7        |

| Altera DSP Builder Setup                       | 1-8        |

| Xilinx FPGA Floating-Point Library Setup       | 1-8        |

| Supported Third-Party Tools and Hardware       | 1-9        |

| Third-Party Synthesis Tools                    | 1-9        |

| FPGA-in-the-Loop Hardware                      | 1-9        |

| xPC Target FPGA I/O Hardware                   | 1-10       |

| FPGA Turnkey Hardware                          | 1-10       |

| VHDL and Verilog Language Support              | 1-12       |

#### **Tutorials**

# 2

1

| HDL Code Generation from a MATLAB Algorithm | 2-2 |

|---------------------------------------------|-----|

| About the Algorithm in This Example         | 2-2 |

| Copying Files Locally                       | 2-4 |

| Setting Up Your C Compiler                  | 2-4 |

| Checking Your Synthesis Tool Setup          | 2-5 |

| Testing the Original MATLAB Algorithm       | 2-5 |

| Setting Up an HDL Coder Project                         | 2-7    |

|---------------------------------------------------------|--------|

| Creating Fixed-Point Versions of the Algorithm and Test |        |

| Bench                                                   | 2-9    |

| Generating HDL Code                                     | 2-14   |

|                                                         |        |

| HDL Code Generation from a Simulink Model               | 2-17   |

|                                                         |        |

| Before You Generate Code                                | 2 - 17 |

| Overview of Exercises                                   | 2-18   |

| The sfir_fixed Model                                    | 2-18   |

| Generate Code Using the HDL Workflow Advisor            | 2 - 21 |

| Generate HDL Code Using the Command Line                | 2-36   |

| Generate HDL Code Using the Configuration Parameters    |        |

| Dialog Box                                              | 2-44   |

| Simulating and Verifying Generated HDL Code             | 2-55   |

|                                                         |        |

# Index

# Getting Started with HDL Coder

- "HDL Coder Product Description" on page 1-2

- "Prepare Simulink Model For HDL Code Generation" on page 1-3

- "Tool Setup" on page 1-4

- "Supported Third-Party Tools and Hardware" on page 1-9

- "VHDL and Verilog Language Support" on page 1-12

# **HDL Coder Product Description**

#### Generate VHDL® and Verilog® code for FPGA and ASIC designs

HDL Coder<sup>™</sup> generates portable, synthesizable VHDL and Verilog code from MATLAB<sup>®</sup> functions, Simulink<sup>®</sup> models, and Stateflow<sup>®</sup> charts. The generated HDL code can be used for FPGA programming or ASIC prototyping and design.

HDL Coder provides a workflow advisor that automates the programming of Xilinx<sup>®</sup> and Altera<sup>®</sup> FPGAs. You can control HDL architecture and implementation, highlight critical paths, and generate hardware resource utilization estimates. HDL Coder provides traceability between your Simulink model and the generated Verilog and VHDL code, enabling code verification for high-integrity applications adhering to DO-254 and other standards.

#### **Key Features**

- Target-independent, synthesizable VHDL and Verilog code

- Code generation support for MATLAB functions, System objects and Simulink blocks

- Mealy and Moore finite-state machines and control logic implementations using Stateflow

- Workflow advisor for programming Xilinx and Altera application boards

- Resource sharing and retiming for area-speed tradeoffs

- Code-to-model and model-to-code traceability for DO-254

- Legacy code integration

# **Prepare Simulink Model For HDL Code Generation**

To prepare your Simulink model for code generation:

• Use checkhdl to check that blocks in your model are supported for HDL code generation.

You can save time by creating your model using blocks from the hdlsupported library, which you generate using hdllib. However, not all available combinations of supported blocks, block implementations, block properties, and HDL optimizations are supported for code generation. checkhdl can find many code generation incompatibilities, but you may need to modify your model later, to generate code that meets your hardware requirements.

• If you want to synthesize your generated HDL code, convert your model to fixed point.

To learn how to use Fixed-Point Designer<sup>™</sup> to convert your floating-point model to fixed-point, see "Convert Floating-Point Model to Fixed Point".

You can synthesize some floating-point constructs if your synthesis tool and hardware support it. To learn more, see "FPGA Floating-Point Libraries".

• Run hdlsetup to configure the solver for HDL code generation.

# **Tool Setup**

# In this section...

"C/C++ Compiler Setup" on page 1-4

"Synthesis Tool Path Setup" on page 1-4

"HDL Simulator Setup" on page 1-7

"Xilinx System Generator Setup" on page 1-7

"Altera DSP Builder Setup" on page 1-8

"Xilinx FPGA Floating-Point Library Setup" on page 1-8

## C/C++ Compiler Setup

HDL Coder requires a C/C++ compiler in order to compile the test bench for faster simulation.

Before using HDL Coder, you must set up your C/C++ compiler by running the mex -setup command, as described in the documentation for mex in the MATLAB Function Reference. You must run this command even if you use the default C compiler that comes with the MATLAB product for Microsoft<sup>®</sup> Windows<sup>®</sup> platforms. You can also use mex to choose and configure a different C/C++ compiler, as described in "Build MEX-Files", in the MATLAB External Interfaces documentation.

For a list of supported compilers, see at http://www.mathworks.com/support/compilers/current\_release/.

**Note** The LCC compiler is not supported in the current release. Please use one of the other compilers in the list at http://www.mathworks.com/support/compilers/current\_release/.

# Synthesis Tool Path Setup

- "hdlsetuptoolpath command" on page 1-5

- "Add Synthesis Tool for Current MATLAB Session" on page 1-6

• "Check Your Synthesis Tool Setup" on page 1-6

#### hdlsetuptoolpath command

To use HDL Coder with one of the supported third-party FPGA synthesis tools, you must add the tool to your system path using the hdlsetuptoolpath command before opening the HDL Workflow Advisor. If you already have the HDL Workflow Advisor open, see "Add Synthesis Tool for Current MATLAB Session" on page 1-6.

The syntax of hdlsetuptoolpath is:

```

hdlsetuptoolpath ('ToolName', TOOLNAME, 'ToolPath', TOOLPATH)

```

The input name-value pairs are:

| Name       | Value                                  | Description                                                               |

|------------|----------------------------------------|---------------------------------------------------------------------------|

| 'ToolName' | 'Xilinx ISE' or<br>'Altera Quartus II' | Specifies the synthesis tool name.                                        |

| 'ToolPath' | 'full_path_to_executa                  | b <b>Sp</b> ecifies the full path<br>to the synthesis tool<br>executable. |

For example, the following command sets the synthesis tool path to point to an installed Xilinx ISE 13.1 executable.

```

hdlsetuptoolpath('ToolName','Xilinx ISE', ...

'ToolPath', 'C:\Xilinx\13.1\ISE DS\ISE\bin\nt64\ise.exe');

```

If you have an icon for the synthesis tool on your Windows desktop, to find the tool path:

**1** Right-click the icon and select **Properties**.

2 Click the **Shortcut** tab.

**Tip** hdlsetuptoolpath changes the system path and system environment variables for the current MATLAB session only. To execute hdlsetuptoolpath automatically when MATLAB starts, add hdlsetuptoolpath to your startup.m script.

#### Add Synthesis Tool for Current MATLAB Session Simulink to HDL Workflow

- 1 Close the HDL Workflow Advisor.

- **2** Use the "hdlsetuptoolpath command" on page 1-5 to add the synthesis tool path.

- 3 Open the HDL Workflow Advisor.

The synthesis tool is now available.

#### MATLAB to HDL Workflow

- 1 At the MATLAB command line, use the "hdlsetuptoolpath command" on page 1-5 to add the synthesis tool.

- 2 In the HDL Workflow Advisor, in the Select Code Generation Target step, to the right of Synthesis tool, click Refresh list.

The synthesis tool is now available.

#### **Check Your Synthesis Tool Setup**

To check your Xilinx ISE synthesis tool setup in MATLAB, try launching the tool with the following command:

!ise

To check your Altera Quartus synthesis tool setup in MATLAB, try launching the tool with the following command:

!quartus

#### **HDL Simulator Setup**

#### HDL Simulator Setup For Use With MATLAB

To set up ModelSim<sup>®</sup>, Questa<sup>®</sup>, or Incisive<sup>®</sup> for HDL simulation, or for cosimulation with HDL Verifier<sup>TM</sup>, see "Start HDL Simulator".

#### HDL Simulator Setup For Use With Simulink

To set up ModelSim, Questa, or Incisive for HDL simulation, or for cosimulation with HDL Verifier, see "Start HDL Simulator".

### **Xilinx System Generator Setup**

To generate ModelSim simulation scripts for a design containing Xilinx System Generator blocks, you must:

- Have compiled Xilinx simulation libraries.

- Specify the path to your compiled libraries.

#### **Required Libraries**

You must have the following compiled Xilinx simulation libraries for your EDA simulator and target language to generate ModelSim simulation scripts:

- unisim

- simprim

- xilinxcorelib

Refer to the Xilinx documentation for compxlib to learn how to compile these libraries.

#### **Specify Path to Required Libraries**

Specify the path to your compiled Xilinx simulation libraries by setting the XilinxSimulatorLibPath parameter for your model.

For example, you can use hdlset\_param to set XilinxSimulatorLibPath:

libpath = '/apps/Xilinx\_ISE/XilinxISE-13.4/Linux/ISE\_DS/ISE/vhdl/

```

mti_se/6.6a/lin64/xilinxcorelib';

hdlset_param (bdroot, 'XilinxSimulatorLibPath', libpath);

```

#### Altera DSP Builder Setup

To generate code for a design containing both Altera DSP Builder and Simulink blocks, you must open MATLAB with Altera DSP Builder. Refer to the Altera DSP Builder documentation for details.

#### Xilinx FPGA Floating-Point Library Setup

To map your design to a Xilinx floating-point library, you must:

- Use Xilinx LogiCORE IP Floating-Point Operator v5.0.

- Have the compiled xilinxcorelib simulation library for your EDA simulator and target language.

Refer to the Xilinx compxlib documentation to learn how to compile this library.

• Specify the path to your compiled Xilinx simulation libraries by setting the XilinxSimulatorLibPath parameter for your DUT.

For example, you can use hdlset\_param to set XilinxSimulatorLibPath:

```

myDUT = gcb;

libpath = '/apps/Xilinx_ISE/XilinxISE-13.4/Linux/ISE_DS/ISE/vhdl/

mti_se/6.6a/lin64/xilinxcorelib';

hdlset_param (myDUT, 'XilinxSimulatorLibPath', libpath);

```

# Supported Third-Party Tools and Hardware

#### In this section...

"Third-Party Synthesis Tools" on page 1-9

"FPGA-in-the-Loop Hardware" on page 1-9

"xPC Target FPGA I/O Hardware" on page 1-10

"FPGA Turnkey Hardware" on page 1-10

#### **Third-Party Synthesis Tools**

The HDL Workflow Advisor is tested with the following third-party FPGA synthesis tools:

- Xilinx ISE 14.4

- Altera Quartus II 12.1 SP1

- Xilinx ISE 10.1 is supported only for compatibility with Speedgoat FPGA target devices.

Speedgoat IO301, IO303, and IO311 FPGA IO boards, which use Xilinx Virtex-II FPGAs, are tested with Xilinx ISE version 10.1. Before you select one of these Speedgoat devices in the HDL Workflow Advisor, make sure that you have installed Xilinx ISE 10.1. See "Generate xPC Target<sup>TM</sup> Interface for Speedgoat Boards" for more information.

For FPGA-in-the-Loop or Customization for USRP<sup>®</sup> Device using the HDL Workflow Advisor, a supported synthesis tool must be installed, and the synthesis tool executable must be on the system path.

#### FPGA-in-the-Loop Hardware

The FPGAs supported for FPGA-in-the-loop simulation with HDL Verifier are listed in the HDL Verifier documentation. See "Preregistered FPGA Devices for FIL Simulation" for details.

You can also add custom FPGA boards using the FPGA Board Manager. See "FPGA Board Customization" for details.

#### xPC Target FPGA I/O Hardware

The FPGA I/O boards supported for use with the xPC Target FPGA IO workflow are listed in the xPC Target documentation. See "FPGA Support" for details.

#### **FPGA Turnkey Hardware**

The following hardware is supported for the FPGA Turnkey workflow:

- Altera Arria II GX FPGA development kit

- Altera Cyclone III FPGA development kit

- Altera Cyclone IV GX FPGA development kit

- Altera DE2-115 development and education board

- XUP Atlys Spartan-6 development board

- Xilinx Spartan-3A DSP 1800A development board

- Xilinx Spartan-6 SP605 development board

- Xilinx Virtex-4 ML401 development board

- Xilinx Virtex-4 ML402 development board

- Xilinx Virtex-5 ML506 development board

- Xilinx Virtex-6 ML605 development board

For FPGA development boards that have more than one FPGA device, only one such device can be used with FPGA Turnkey.

#### Supported FPGA Device Families for Board Customization

You can also add custom FPGA boards using the FPGA Board Manager. HDL Coder supports the following FPGA device families for board customization; that is, when you create your own board definition file. See "FPGA Board Customization".

| Device Family |                          |  |

|---------------|--------------------------|--|

| Xilinx        | Kintex7                  |  |

|               | Spartan-3A DSP           |  |

|               | Spartan3                 |  |

|               | Spartan3A and Spartan3AN |  |

|               | Spartan3E                |  |

|               | Spartan6                 |  |

|               | Virtex4                  |  |

|               | Virtex5                  |  |

|               | Virtex6                  |  |

|               | Virtex7                  |  |

| Altera        | Cyclone III              |  |

|               | Cyclone IV               |  |

|               | Arria II                 |  |

|               | Stratix IV               |  |

|               | Stratix V                |  |

1

# **VHDL and Verilog Language Support**

The generated HDL code complies with the following standards:

- VHDL-1993 (IEEE<sup>®</sup> 1076-1993) or later

- Verilog-2001 (IEEE 1364-2001) or later

# Tutorials

- "HDL Code Generation from a MATLAB Algorithm" on page 2-2

- "HDL Code Generation from a Simulink Model" on page 2-17

# HDL Code Generation from a MATLAB Algorithm

#### In this section ...

"About the Algorithm in This Example" on page 2-2

"Copying Files Locally" on page 2-4

"Setting Up Your C Compiler" on page 2-4

"Checking Your Synthesis Tool Setup" on page 2-5

"Testing the Original MATLAB Algorithm" on page 2-5

"Setting Up an HDL Coder Project" on page 2-7

"Creating Fixed-Point Versions of the Algorithm and Test Bench" on page 2-9

"Generating HDL Code" on page 2-14

### About the Algorithm in This Example

For the purpose of this example, you generate and synthesize HDL code for a MATLAB algorithm that implements a simple filter. However, you can use HDL Coder to generate HDL code from MATLAB algorithms for many applications.

This tutorial uses these files:

- mlhdlc\_sfir.m Simple filter function from which you generate HDL code.

- mlhdlc\_sfir\_tb.m Test bench that the HDL Coder project uses to exercise the filter using a representative input range.

#### mlhdlc\_sfir Function Code

The following code provides the complete mlhdlc\_sfir function definition.

%#codegen

```

function [y_out, delayed_xout] = mlhdlc_sfir(x_in, h_in1, h_in2, h_in3, h_in4)

% Symmetric FIR Filter

```

```

persistent ud1 ud2 ud3 ud4 ud5 ud6 ud7 ud8;

if isempty(ud1)

ud1 = 0; ud2 = 0; ud3 = 0; ud4 = 0; ud5 = 0; ud6 = 0; ud7 = 0; ud8 = 0;

end

a1 = ud1 + ud8; a2 = ud2 + ud7;

a3 = ud3 + ud6; a4 = ud4 + ud5;

m1 = h in1 * a1; m2 = h in2 * a2;

m3 = h_in3 * a3; m4 = h_in4 * a4;

a5 = m1 + m2; a6 = m3 + m4;

% filtered output

y_{out} = a5 + a6;

% delayout input signal

delayed_xout = ud8;

% update the delay line

ud8 = ud7;

ud7 = ud6;

ud6 = ud5;

ud5 = ud4;

ud4 = ud3;

ud3 = ud2;

ud2 = ud1;

ud1 = x in;

```

end

#### mlhdlc\_sfir\_tb.m Test Bench

The mlhdlc\_sfir\_tb test bench creates an input signal and calls the mlhdlc\_sfir filter, passing in the input data.

```

clear all;

% input signal with noise

x_in = cos(2.*pi.*(0:0.001:2).*(1+(0:0.001:2).*75)).';

```

```

% filter coefficients

h1 = -0.1339; h2 = -0.0838; h3 = 0.2026; h4 = 0.4064;

len = length(x_in);

y_out = zeros(1,len);

for ii=1:len

data = x_in(ii);

% call to the design 'mlhdlc_sfir' that is targeted for hardware

[y_out(ii), x_out(ii)] = mlhdlc_sfir(data, h1, h2, h3, h4);

end

figure('Name', [mfilename, '_plot']);

subplot(2,1,1); plot(1:len,x_in);

subplot(2,1,2); plot(1:len,y out);

```

#### **Copying Files Locally**

Before you begin generating code, set up a working folder and copy the tutorial files to this folder.

- 1 Start MATLAB.

- 2 Create a folder named filter\_sfir, for example:

mkdir filter\_sfir

The folder must not be within the MATLAB directory structure. You must be able to write to this folder.

**3** Copy the tutorial files, mlhdlc\_sfir.m and mlhdlc\_sfir\_tb.m, to this folder.

#### **Setting Up Your C Compiler**

Before using HDL Coder to generate HDL code, you must set up your C compiler.

**Note** If your installation does not include a default compiler, for a list of supported compilers for the current release of MATLAB, see at http://www.mathworks.com/support/compilers/current\_release/. Install a compiler that is suitable for your platform.

To set up the installed compiler:

1 At the MATLAB command line, enter:

mex -setup

- 2 Enter y to see the list of installed compilers.

- **3** Select a supported compiler.

- 4 Enter y to verify your choice.

#### **Checking Your Synthesis Tool Setup**

Before using HDL Coder to synthesize HDL code, you must set up your synthesis tool path.

To check your Xilinx ISE synthesis tool setup, try launching the tool with the following command:

!ise

To check your Altera Quartus synthesis tool setup, try launching the tool with the following command:

!quartus

If the tool does not open, or opens the wrong version, see "Synthesis Tool Path Setup" on page 1-4.

#### **Testing the Original MATLAB Algorithm**

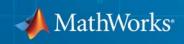

Before generating HDL code for this MATLAB algorithm, simulate your MATLAB design to verify that it runs, and to provide a baseline for comparison with the generated HDL code.

- 1 Make the filter\_sfir folder your working folder, for example: cd filter\_sfir

- 2 Run the test bench. At the MATLAB command line, enter: mlhdlc\_sfir\_tb

The test bench runs and plots the input signal and the filtered output.

### Setting Up an HDL Coder Project

- 1 On the Apps tab, on the far right of the Apps section, click the arrow .

- 2 Under Code Generation, click HDL Coder.

**3** Enter mydesign for the project name.

HDL Coder creates the project, mydesign.prj, in the local working folder, and opens the project in the right side of the MATLAB workspace.

| HDL Code Generation 💿                                                                                           |

|-----------------------------------------------------------------------------------------------------------------|

| 🔄 mydesign.prj 🔹 🛗 🔘 🔹                                                                                          |

| MATLAB Function                                                                                                 |

| Specify the top-level MATLAB design function (Design Under Test).                                               |

| Add only the file that you would call directly from MATLAB. Do not add files that are called by this function.  |

| Add MATLAB function                                                                                             |

| MATLAB Test Bench                                                                                               |

| Specify the top-level MATLAB test script or function that calls the MATLAB design function.                     |

| Add only the file that you would call directly from MATLAB. Do not add files that are called by this test file. |

| Add files                                                                                                       |

| Specify your design function and test bench above, then use the<br>Workflow Advisor to generate code.           |

4 Under MATLAB Function, click Add MATLAB function.

**5** In the Add Files dialog box, select mlhdlc\_sfir.m and click **Open**.

HDL Coder adds the file to the project.

- 6 Under MATLAB Test Bench, click Add MATLAB test bench.

- 7 In the Add Files dialog box, select mlhdlc\_sfir\_tb.m and click Open.

HDL Coder adds the test bench file to the project.

You are now ready to convert the code from floating-point to fixed-point.

# Creating Fixed-Point Versions of the Algorithm and Test Bench

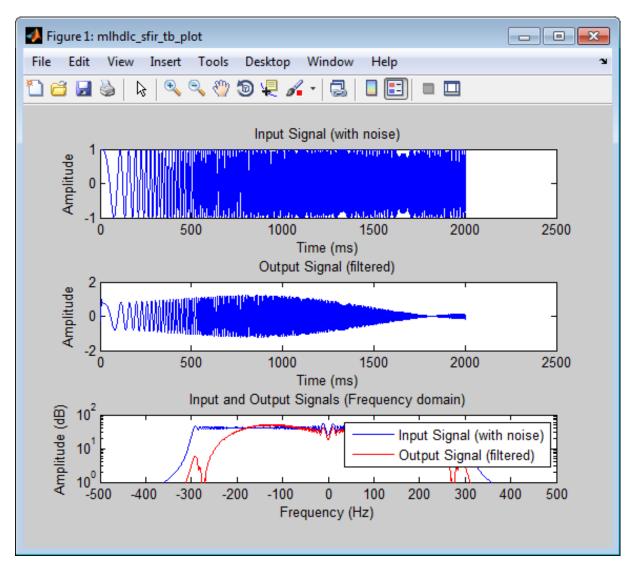

**1** In the project, at the bottom of the pane, click the **Workflow Advisor** button to open the HDL Coder Workflow Advisor.

| A UDL Code Constantion                                                                     |                        |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                            |                        |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Define Input Types     Fixed-Point Conversion     HDL Code Generation     HDL Verification | oating-point MATLAB de | nerate synthesizable HDL code from y<br>esign to fixed-point based on your sele<br>Convert to fixed-point at build time •<br>Project folder • | The second secon |

2 Select the Define Input Types task and click Run.

The coder simulates the algorithm and test bench, and automatically defines input types.

**3** On the left, select the **Fixed-Point Conversion** task. The Fixed-Point Conversion tool opens in the right pane.

After the simulation, each input, output, and persistent variable has a **Sim Min**, **Sim Max**, and **Proposed Type** in the table.

When proposing fraction lengths for floating-point data types, the coder uses the **Default word length**. In this tutorial, the **Default word length** is 14. The advisor provides a default **Safety Margin for Simulation Min/Max** of 4%. The advisor adjusts the range of the data by this safety factor. For example, a value of 4 specifies that you want a range of at least 4 percent larger.

In this example, we use only the simulation ranges to infer fixed-point types. **Compute Derived Ranges** gives you the option of using static range analysis. To learn more about options in the fixed-point conversion workflow, see "Automated Fixed-Point Conversion".

**b** At the top, in the Verification section, click **Validate Types**.

The coder validates the build with the proposed fixed-point types and generates a fixed-point design.

c At the top, in the Verification section, click the down-arrow for Test Numerics and select Log inputs and outputs for comparison plots. Click the top part of the Test Numerics button.

The coder simulates the fixed-point design with the original test bench compares the output to the original floating-point design output.

d Click the down-arrow to the right of the Verification Output tab and select Type Validation Output. Click mlhdlc\_sfir\_fixpt to see the fixed-point MATLAB code for the mlhdlc\_sfir function.

```

%#codegen

function [y_out,delayed_xout] = mlhdlc_sfir_fixpt(x_in,h_in1,h_in2,h_in3,h_in4)

fm = fimath('RoundingMethod', 'Floor', 'OverflowAction', 'Wrap', 'ProductMode',

'FullPrecision', 'MaxProductWordLength', 128, 'SumMode', 'FullPrecision',

'MaxSumWordLength', 128);

% Symmetric FIR Filter

% declare and initialize the delay registers

persistent ud1 ud2 ud3 ud4 ud5 ud6 ud7 ud8

if isempty( ud1 )

ud1 = fi(0, 1, 14, 12, fm);

```

```

ud2 = fi(0, 1, 14, 12, fm);

ud3 = fi(0, 1, 14, 12, fm);

ud4 = fi(0, 1, 14, 12, fm);

ud5 = fi(0, 1, 14, 12, fm);

ud6 = fi(0, 1, 14, 12, fm);

ud7 = fi(0, 1, 14, 12, fm);

ud8 = fi(0, 1, 14, 12, fm);

end

% access the previous value of states/registers

a1 = fi(ud1 + ud8, 1, 14, 11, fm);

a2 = fi(ud2 + ud7, 1, 14, 11, fm);

a3 = fi(ud3 + ud6, 1, 14, 11, fm);

a4 = fi(ud4 + ud5, 1, 14, 11, fm);

% multiplier chain

m1 = fi(h_in1*a1, 1, 14, 14, fm);

m2 = fi(h in2*a2, 1, 14, 15, fm);

m3 = fi(h_in3*a3, 1, 14, 14, fm);

m4 = fi(h in4*a4, 1, 14, 13, fm);

% adder chain

a5 = fi(m1 + m2, 1, 14, 14, fm);

a6 = fi(m3 + m4, 1, 14, 12, fm);

% filtered output

y_out = fi(a5 + a6, 1, 14, 12, fm);

% delayout input signal

delayed xout = fi(ud8, 1, 14, 12, fm);

% update the delay line

ud8 = fi(ud7, 1, 14, 12, fm);

ud7 = fi(ud6, 1, 14, 12, fm);

ud6 = fi(ud5, 1, 14, 12, fm);

ud5 = fi(ud4, 1, 14, 12, fm);

ud4 = fi(ud3, 1, 14, 12, fm);

ud3 = fi(ud2, 1, 14, 12, fm);

ud2 = fi(ud1, 1, 14, 12, fm);

ud1 = fi(x in, 1, 14, 12, fm);

end

```

e Click the View report link.

You can explore the fixed-point code further in the Code Generation Report.

#### **Generating HDL Code**

**1** In the HDL Workflow Advisor left pane, select **HDL Code Generation** and click **Run** to generate HDL code with the default options.

The message window has a links to the generated HDL code and the resource report. Click the links to view the code and resource report.

**Tip** You can use the **Target**, **Coding Style**, **Clocks and Ports**, **Optimizations**, **Advanced**, and **Script Options** tabs to set code generation options. To learn about the options, click the ? button.

- 2 In the HDL Workflow Advisor left pane, select HDL Verification > Verify with HDL Test Bench.

- **3** Enable **Generate HDL test bench** and disable **Skip this step**. Enable **Simulate generated HDL test bench** and select a simulation tool. Click **Run**.

The task generates an HDL test bench, then simulates the fixed-point design using the selected simulation tool, and generates a compilation report and a simulation report.

| A HDL Code Generation                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - • • |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 🖃 🤡 HDL Workflow Advisor                                                                                                                                                                                                                                                  | Verify the HDL code with test vectors from the test bench using the specified simulation tool.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| HDL Workflow Advisor<br>HDL Workflow Advisor<br>Fixed-Point Conversion<br>HDL Code Generation<br>HDL Verification<br>Verify with HDL Test Bench<br>Verify with FDGA-in-the-Loop<br>Synthesis and Analysis<br>Create Project<br>Run Logic Synthesis<br>Run Place and Route | Output Settings     Test Bench Options       HDL Test Bench Generation Settings       Image: Comparison of the set of |       |

|                                                                                                                                                                                                                                                                           | <pre>Skip this Step ### Begin TestBench generation. ### Collecting data ### Begin HDL test bench file generation with logged samples ### Generating test bench: mlhdlc_sfir_FixPt_tb.vhd ### Creating stimulus vectors ### Simulating the design 'mlhdlc_sfir_FixPt' using 'ModelSim'. ### Generating Compilation Report mlhdlc_sfir_FixPt_vsim_log_compile.txt ### Generating Simulation Report mlhdlc_sfir_FixPt_vsim_log_sim.txt ### Elapsed Time: 199.9228 sec(s)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2 Run |

- 4 Click Synthesis and Analysis and disable Skip this step.

- a Select Create Project.

- **b** On the right, select a **Synthesis tool** from the list and click **Run**.

This task creates a synthesis project for the HDL code. HDL Coder uses this project in the next task to synthesize the design.

5 Select and run Run Logic Synthesis.

This task:

• Launches the synthesis tool in the background.

- Opens the synthesis project created in the previous task, compiles HDL code, synthesizes the design, and emits netlists and related files.

- Generates a synthesis report.

- 6 Select and run Place and Route.

This task:

- Launches the synthesis tool in the background.

- Runs a Place and Route process that takes the circuit description produced by the previous mapping process, and emits a circuit description suitable for programming an FPGA.

- Emits pre- and post-routing timing information for use in critical path analysis and back annotation of your source model.

- Displays results.

## HDL Code Generation from a Simulink Model

#### In this section ...

"Before You Generate Code" on page 2-17

"Overview of Exercises" on page 2-18

"The sfir\_fixed Model" on page 2-18

"Generate Code Using the HDL Workflow Advisor" on page 2-21

"Generate HDL Code Using the Command Line" on page 2-36

"Generate HDL Code Using the Configuration Parameters Dialog Box" on page 2-44

"Simulating and Verifying Generated HDL Code" on page 2-55

#### **Before You Generate Code**

Before you generate HDL code from your own models, you should do the following:

- Before generating code, use the hdlsetup utility (described in "Initializing Model Parameters with hdlsetup" on page 2-37) to set up your model for HDL code generation quickly and consistently.

- Use the hdllib utility to create a library of blocks that are currently supported for HDL code generation, as described in "Create a Supported Blocks Library". By constructing models with blocks from this library, your models will be HDL compatible.

The set of supported blocks will change in future releases, so you should rebuild your supported blocks library each time you install a new version of this product.

• Use the **Run Compatibility Checker** option (described in "Selecting and Checking a Subsystem for HDL Compatibility" on page 2-50) to check HDL compatibility of your model or DUT and generate an HDL Code Generation Check Report.

Alternatively, you can invoke the checkhdl function (see checkhdl) to run the compatibility checker.

#### **Overview of Exercises**

The coder supports HDL code generation in your choice of environments:

- The MATLAB Command Window supports code generation using the makehdl, makehdltb, and other functions.

- The Simulink GUI (the Configuration Parameters dialog box and/or Model Explorer) provides an integrated view of the model simulation parameters and HDL code generation parameters and functions.

The hands-on exercises in this chapter introduce you to the mechanics of generating and simulating HDL code, using the same model to generate code in both environments. In a series of steps, you will

- Configure a simple model for code generation.

- Generate VHDL code from a subsystem of the model.

- Generate a VHDL test bench and scripts for the Mentor Graphics<sup>®</sup> ModelSim simulator to drive a simulation of the model.

- Compile and execute the model and test bench code in the simulator.

- Generate and simulate Verilog code from the same model.

- Check a model for compatibility with the coder.

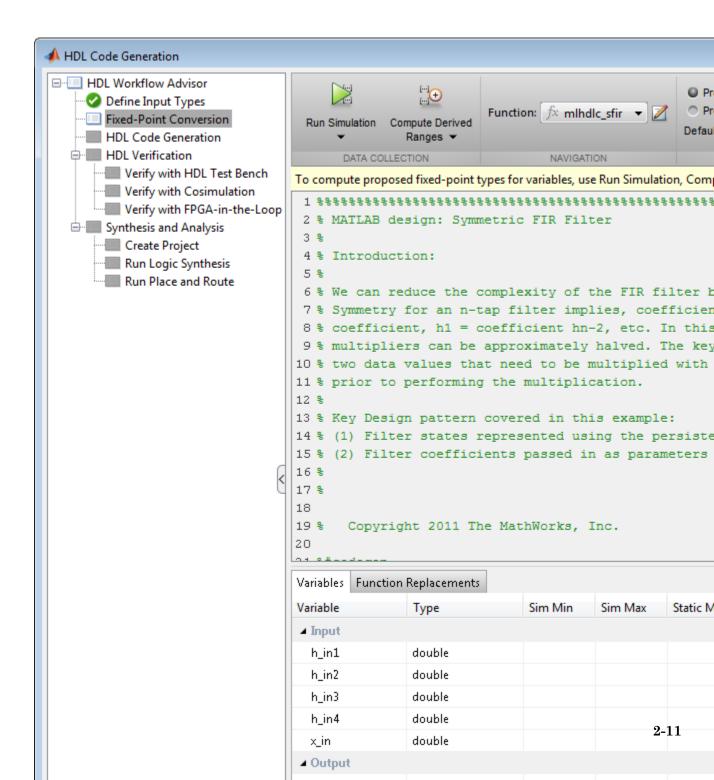

#### The sfir\_fixed Model

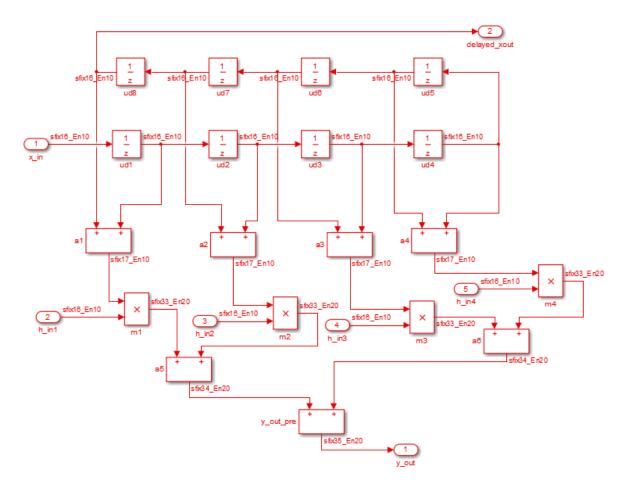

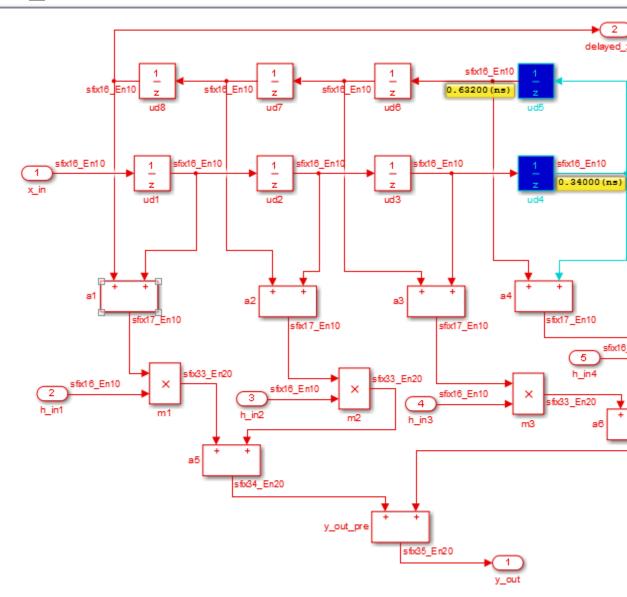

These exercises use the sfir\_fixed model as a source for HDL code generation. The model simulates a symmetric finite impulse response (FIR) filter algorithm, implemented with fixed-point arithmetic.

The blocks in this example model support HDL code generation, and the model parameters have been configured for HDL code generation. The following figure shows the top level of the model.

This model uses a division of labor that is helpful in HDL design:

- The symmetric\_fir subsystem, which implements the filter algorithm, is the device under test (DUT). An HDL entity will be generated, tested, and eventually synthesized from this subsystem.

- The top-level model components that drive the subsystem work as a test bench.

The top-level model generates 16-bit fixed-point input signals for the symmetric\_fir subsystem. The Signal From Workspace block generates a

test input (stimulus) signal for the filter. The four Constant blocks provide filter coefficients.

The Scope blocks are used in simulation only. They are virtual blocks, and do not generate HDL code.

The following figure shows the symmetric\_fir subsystem.

The fixed-point data types propagate through the subsystem. Inputs inherit the data types of the signals presented to them. Where required, internal

rules of the blocks determine the output data type, given the input data types and the operation performed (for example, the Product blocks).

The filter outputs a fixed-point result at the y\_out port, and also replicates its input (after passing it through several delay stages) at the delayed\_x\_out port.

In the exercises that follow, you generate VHDL code that implements the symmetric\_fir subsystem as an entity. You then generate a test bench from the top-level model. The test bench drives the generated entity, for the required number of clock steps, with stimulus data generated from the Signal From Workspace block.

# Generate Code Using the HDL Workflow Advisor

This example shows how to generate HDL code from a Simulink model using the HDL Workflow Advisor.

- "Before You Begin" on page 2-21

- "Create Working Folder and Copy Model" on page 2-21

- "Generate Code Using the HDL Workflow Advisor" on page 2-22

- "Perform FPGA Synthesis and Analysis" on page 2-33

## **Before You Begin**

This example uses the Xilinx ISE synthesis tool, and assumes your synthesis tool path is set up. You can also follow this example using Altera Quartus II. To learn how to set up your synthesis tool path, see "Synthesis Tool Path Setup" on page 1-4.

The model you use in this example, sfir\_fixed, is already prepared for code generation. To learn more about preparing your model for code generation, see "Prepare Simulink Model For HDL Code Generation" on page 1-3.

## **Create Working Folder and Copy Model**

Start MATLAB.

Create a folder named sl\_hdlcoder\_work. For example:

```

mkdir C:\work\sl_hdlcoder_work

```

You will use sl\_hdlcoder\_work to store a local copy of the example model and to store folders and code generated by the coder. The location of the folder does not matter, except that it should not be within the MATLAB folder tree.

Make the sl\_hdlcoder\_work folder your working folder. For example:

cd C:\work\sl\_hdlcoder\_work

Open the sfir\_fixed model.

sfir\_fixed

Save a copy of sfir\_fixed in your sl\_hdlcoder\_work folder.

#### Generate Code Using the HDL Workflow Advisor

Right-click the symmetric\_fir subsystem and select HDL Code > HDL Workflow Advisor.

In the **Set Target > Set Target Device and Synthesis Tool** step, for **Synthesis tool**, select **Xilinx ISE** and click **Run This Task**.

| HDL Workflow Advisor - sfir_fixed/symmetric_fir                                                                                                                       |                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File Edit Run Settings Help                                                                                                                                           |                                                                                                                                                                                                                                                      |

| Find: 🗾 🔶 🖒                                                                                                                                                           |                                                                                                                                                                                                                                                      |

| <ul> <li>IDE Workflow Advisor</li> <li>ISE Target</li> <li>1. Set Target Device and Synthesis Tool</li> <li>IDE ATT AND ADD ADD ADD ADD ADD ADD ADD ADD ADD</li></ul> | <b>1.1. Set Target Device and Synthesis Tool</b> Analysis (^Triggers Update Diagram)         Set Target Device and Synthesis Tool for HDL code generation         Input Parameters       Target workflow: Generic ASIC/FPGA         Target platform: |

Right-click **Prepare Model For HDL Code Generation** and select **Run to Failure**. The HDL Workflow Advisor checks the model for code generation compatibility.

| HDL Workflow Advisor - sfir_fixed/symmetric_fir                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File Edit Run Settings Help                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                |

| Find: 🗸 🗘                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                |

| <ul> <li>HDL Workflow Advisor</li> <li>I Set Target</li> <li>1. Set Target Device and Synthesis Tool</li> <li>I Set Target Model For HDL Code Generation</li> <li>2. Prepare Model For HDL Code Generation</li> <li>2.1. Check Global Settings</li> <li>2.2. Check Algebraic Loops</li> <li>2.2. Check Block Compatibility</li> <li>2.2.3. Check Block Compatibility</li> <li>2.2.4. Check Sample Times</li> <li>IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII</li></ul> | Analysis (^Triggers Update Diagram)         Check model for global sample time settings         Input Parameters         Ignore warnings         Result:       Image: Passed         Passed Running Check Sample Times passed. |

In the HDL Code Generation > Set Code Generation Options > Set Basic Options step, select the following options, then click Apply:

- For Language, select Verilog.

- Enable Generate traceability report.

- Enable Generate resource utilization report.

| HDL Workflow Advisor - sfir_fixed/symmetric_fir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File Edit Run Settings Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                |

| Find: 🗸 🔶                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                |

| <ul> <li>HDL Workflow Advisor</li> <li>I. Set Target</li> <li>1. Set Target Device and Synthesis Tool</li> <li>I. Set Target Device and Synthesis Tool</li> <li>I. Set Target Device and Synthesis Tool</li> <li>I. Set Target Model For HDL Code Generation</li> <li>2.1. Check Global Settings</li> <li>^2.2. Check Algebraic Loops</li> <li>^2.3. Check Block Compatibility</li> <li>^2.4. Check Sample Times</li> <li>I. Set Code Generation</li> <li>I. Set Code Generation Options</li> <li>I. S. HDL Code Generation Options</li> <li>I. Set Code Generation Options</li> <li>I. Set Advanced Options</li> <li>I. S. Set Advanced Options</li> <li>I. S. Generate RTL Code and Testbench</li> <li>IIII Create Project</li> <li>IIII Create Project</li> <li>IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII</li></ul> | SIL2. Advanced Options  Clock settings  Reset type: Asynchronous  Clock input port: clk  Reset input port: reset Oversampling factor: 1  Additional settings  General Ports Optimization Coding style Balance delays Hierarchical distributed pipelining Optimize timing controller Minimize clock enables  RAM mapping threshold (bits): 256 Max oversampling: Inf Max computation latency: 1 |

| HDL Workflow Advisor - sfir_fixed/symmetric_fir |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File Edit Run Settings Help                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Find: 🗸 🔶                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                 | 3.1.2. Advanced Options         Clock settings         Reset type:       Asynchronous         Clock input port:       clk         Reset input port:       reset         Oversampling factor:       1         Additional settings       General         General       Ports         Optimization       Coding style         Represent constant values by aggregates         Use "rising_edge" for registers         Loop unrolling         Use Verilog `timescale directives         Inline VHDL configuration         Concatenate type safe zeros         Emit time/date stamp in header         HDL coding standard:       None         Scalarize vector ports       Minimize intermediate signals         Include requirements in block comments       Include requirements in block code         Generate parameterized HDL code from masked subsystem |

|                                                 | Initialize all RAM blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                 | RAM Architecture: RAM with clock enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

The code generation report, which includes the resource utilization and traceability reports, opens automatically. The resource utilization report shows the hardware resources your design implementation is using. The traceability report enables you to navigate between your model and the generated code.

| 📔 Code Generation Report    |                                                                              |

|-----------------------------|------------------------------------------------------------------------------|

| Back Forward Search         | HDL Code Generation Report Summary for                                       |

| Contents                    |                                                                              |

| <u>Summary</u>              | Summary                                                                      |

| Clock Summary               |                                                                              |

| Resource Utilization Report | Model                                                                        |

| High-level Resource Report  | Model version                                                                |

| Target-specific Report      | HDL Coder version                                                            |

| Traceability Report         | HDL code generated on                                                        |

|                             | HDL code generated for                                                       |

| Generated Source Files      | Target Language                                                              |

| symmetric_fir.v             | Target Directory                                                             |

|                             | Non-default model properties                                                 |

|                             | Backannotation                                                               |

|                             | HDLSubsystem                                                                 |

|                             | ResourceReport                                                               |

|                             | TargetDirectory                                                              |

|                             | TargetLanguage                                                               |

|                             | Traceability                                                                 |

|                             | Non-default block properties<br>No blocks found with non-default properties. |

## **Perform FPGA Synthesis and Analysis**

In the FPGA Synthesis and Analysis > Perform Synthesis and P/R > Perform Place and Route task, unselect Skip this task and click Apply.

Right-click Annotate Model with Synthesis Result and select Run to Selected Task.

| HDL Workflow Advisor - sfir_fixed/symmetric_fir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|